壓控延遲線工作原理、結(jié)構(gòu)、特點(diǎn)及應(yīng)用全解析

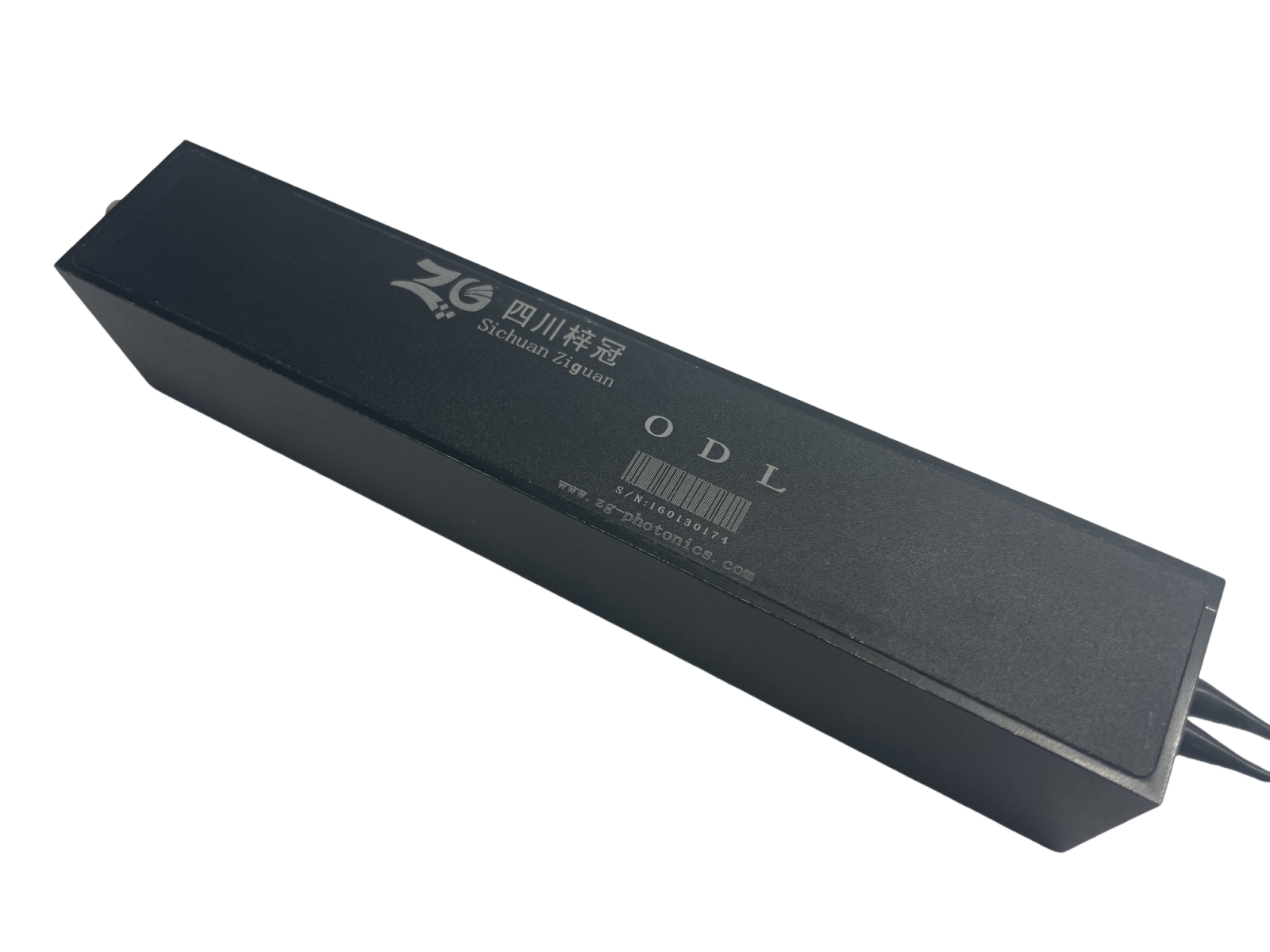

在現(xiàn)代電子系統(tǒng)中,時(shí)鐘信號(hào)的精確同步與控制是確保系統(tǒng)穩(wěn)定運(yùn)行的核心。壓控延遲線(Voltage-Controlled Delay Line,VCDL)作為一種通過電壓調(diào)節(jié)信號(hào)延遲時(shí)間的電路模塊,已成為高速通信、雷達(dá)探測(cè)、芯片測(cè)試等領(lǐng)域的核心技術(shù)。四川梓冠光電將從工作原理、結(jié)構(gòu)特點(diǎn)、應(yīng)用場(chǎng)景及用戶痛點(diǎn)四個(gè)維度,全面解析壓控延遲線的技術(shù)內(nèi)涵。

一、壓控延遲線的工作原理:電壓驅(qū)動(dòng)的延遲調(diào)控

壓控延遲線基于“電壓-延遲”線性映射機(jī)制,通過調(diào)節(jié)控制電壓改變信號(hào)傳播路徑的延遲時(shí)間。其核心結(jié)構(gòu)由多級(jí)延遲單元串聯(lián)組成,每個(gè)單元包含可變電容或電流源,控制電壓的變化會(huì)改變電容充放電速率或電流強(qiáng)度,從而直接調(diào)節(jié)信號(hào)通過時(shí)間。例如,在CMOS工藝中,通過調(diào)整PMOS電流源的柵極電壓,可控制反相器翻轉(zhuǎn)速度,實(shí)現(xiàn)亞皮秒級(jí)延遲精度。

二、壓控延遲線的結(jié)構(gòu):從單元到系統(tǒng)的設(shè)計(jì)邏輯

壓控延遲線的典型結(jié)構(gòu)包含四個(gè)層級(jí):

1、延遲單元:核心模塊,分為差分型與單端型。差分結(jié)構(gòu)采用源極耦合對(duì)管,通過尾電流源控制延遲,具有強(qiáng)共模噪聲抑制能力;單端結(jié)構(gòu)基于反向器改進(jìn),如電流饑餓型延遲單元,通過調(diào)節(jié)負(fù)載電阻實(shí)現(xiàn)延遲控制。

2、級(jí)聯(lián)拓?fù)洌憾嗉?jí)延遲單元串聯(lián)形成延遲鏈,通過級(jí)數(shù)調(diào)節(jié)總延遲范圍。例如,4級(jí)延遲鏈可實(shí)現(xiàn)360°相位覆蓋,滿足時(shí)鐘同步需求。

3、控制接口:包括電荷泵鎖相環(huán)(CP-PLL)或鑒頻鑒相器(PFD),用于生成與參考時(shí)鐘同步的控制電壓。

4、輸出緩沖:通過反相器鏈將延遲信號(hào)整形為標(biāo)準(zhǔn)邏輯電平,確保信號(hào)完整性。

三、壓控延遲線的特點(diǎn):性能與設(shè)計(jì)的權(quán)衡

1、高精度:在先進(jìn)工藝下,單級(jí)延遲單元可實(shí)現(xiàn)<50fs的分辨率,滿足高速串行接口(如PCIe 6.0)的抖動(dòng)要求。

2、線性度:通過優(yōu)化負(fù)載匹配與電流源設(shè)計(jì),可實(shí)現(xiàn)>95%的電壓-延遲線性度,降低系統(tǒng)誤差。

3、抖動(dòng)抑制:采用差分結(jié)構(gòu)與片內(nèi)穩(wěn)壓電源,可將電源噪聲引起的抖動(dòng)控制在<10ps以內(nèi)。

4、面積與功耗:差分結(jié)構(gòu)需雙倍晶體管資源,功耗較單端結(jié)構(gòu)高20%-30%,需根據(jù)應(yīng)用場(chǎng)景權(quán)衡。

四、壓控延遲線的應(yīng)用:從實(shí)驗(yàn)室到工業(yè)場(chǎng)景

1、高速通信:在100G-400G光模塊中,VCDL用于時(shí)鐘數(shù)據(jù)恢復(fù)(CDR),通過精確相位對(duì)齊實(shí)現(xiàn)誤碼率<10^-15。

2、雷達(dá)系統(tǒng):在相控陣?yán)走_(dá)中,VCDL作為時(shí)延補(bǔ)償模塊,通過動(dòng)態(tài)調(diào)節(jié)延遲時(shí)間實(shí)現(xiàn)波束指向的毫秒級(jí)切換。

3、芯片測(cè)試:在ATE設(shè)備中,VCDL用于產(chǎn)生多相位時(shí)鐘,支持并行測(cè)試效率提升50%以上。

4、光通信:在光纖延遲線中,VCDL結(jié)合聲光調(diào)制器,實(shí)現(xiàn)納秒級(jí)延遲調(diào)節(jié),用于光信號(hào)處理。

五、用戶關(guān)心的問題及解決辦法

1、如何選擇合適的壓控延遲線?

用戶在選擇壓控延遲線時(shí),應(yīng)綜合考慮其工作頻率范圍、延遲時(shí)間范圍、線性度、穩(wěn)定性以及成本等因素。同時(shí),還應(yīng)根據(jù)具體應(yīng)用場(chǎng)景的需求,選擇合適的封裝形式和接口類型。

2、如何解決壓控延遲線的非線性問題?

壓控延遲線在實(shí)際應(yīng)用中可能會(huì)遇到非線性問題,即延遲時(shí)間與控制電壓之間不是完全的線性關(guān)系。為了解決這一問題,可以采用預(yù)失真技術(shù)或反饋控制技術(shù)等手段進(jìn)行補(bǔ)償和校正。

3、如何降低壓控延遲線的噪聲和干擾?

壓控延遲線在工作過程中可能會(huì)受到外界噪聲和干擾的影響,從而影響其性能表現(xiàn)。為了降低噪聲和干擾的影響,可以采用屏蔽技術(shù)、濾波技術(shù)或接地技術(shù)等手段進(jìn)行防護(hù)和隔離。

結(jié)語

壓控延遲線作為電子系統(tǒng)中的“時(shí)間雕刻師”,其技術(shù)演進(jìn)正推動(dòng)著通信速率、雷達(dá)精度與測(cè)試效率的極限突破。隨著3D集成、硅光子等技術(shù)的融合,VCDL有望在量子計(jì)算、6G通信等前沿領(lǐng)域發(fā)揮更大價(jià)值。對(duì)于工程師而言,深入理解其工作原理與設(shè)計(jì)方法,是攻克下一代電子系統(tǒng)時(shí)序挑戰(zhàn)的關(guān)鍵。